2019. 8. 5. 14:23ㆍ개발 관련 학습정리/AVR(atmega128) Register 분석

이번엔 atmega128에 있는 SPI (Serial Peripheral Interface Bus) 통신을 알아보도록 하자.

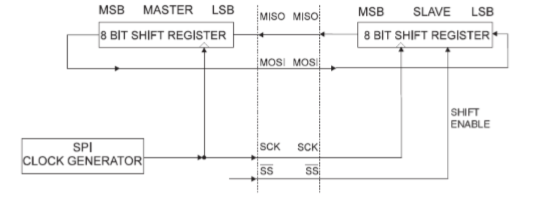

직렬 주변기기 인터페이스 버스라는 뜻으로, 전이중 통신이며 마스터 슬레이브 형식으로 통신한다.

MHz 단위까지 통신이 가능하며 전송완료 인터럽트를 제공한다.

먼저 SS핀으로 슬레이브를 지정하고,

SCK를 통해 송신할 데이터를 시프트 레지스터에 준비하여 마스터에서 슬레이브에게 MOSI를 보내고

슬레이브가 마스터에게 MISO를 보낸다.

레지스터를 알아보자.

1. SPCR (SPI Control Register)

SPIE (SPI Interrupt Enable) : 1로 설정시 전송완료 인터럽트 허용

SPE : (SPI Enable) : 1로 설정시 SPI 통신 허용

DORD (Data ORDer) : 1로 설정시 LSB부터, 0으로 설정시 MSB부터 전송

LSB는 최하위비트, MSB는 최상위 비트를 일컫는 말이다.

MSTR (Master/Slaver Select) : 1로 설정하면 마스터로 동작하고 0으로 하면 슬레이브로 동작한다.

CPOL (Clock POLarity) : SCK 클록의 극성을 설정한다.

CPHA (Clock PHAse) : 데이터 샘플링 동작이 수행되는 SCK 클록의 위상을 설정한다.

0일때, Leading edge의 경우는 샘플링이 되고, Trailing Edge의 경우에는 셋업된다. 1일땐 반대이다.

SPR1..0 (SPi clock Rate select) : SCK 클럭신호의 분주비를 설정한다.

2. SPSR (SPI Status Register)

SPIF (SPi Interrupt Flag) : 전송이 완료되면 1로 세트되면서 인터럽트가 요청된다.

WCOL (Write COLision flag) : SPI를 통해 데이터를 전송하고 있는 동안 SPDR를 기록하려 하면 세트된다.

SPI2X (SPI Double speed) : 마스터 일때 SCK클록 신호 주파수를 2배로 증폭한다.

간단히 세팅하는 예제이다.

void setup() {

DDRB &= ~((1<<PB1)|(1<<PB2)|(1<<PB0)); // SCK, MOSI, SS --> inputs

DDRB |= (1<<PB3); // MISO --> output

//slave mode

SPCR &= ~(1<<MSTR);

//16000KHz / 16

SPCR |= (1<<SPR0);

//enable SPI

SPCR |= ((1<<SPE)|(1<<SPIE));

}

다음에는 UASRT통신에 대해 알아보도록 하겠다.

![[복두출판사]AVR ATmega128 프로그래밍 응용실습:ED-4513 마이크로프로세서 콤보 IT를 이용한, 복두출판사](https://static.coupangcdn.com/image/affiliate/banner/577fb0a8ddb26d4c8ffc130765a1295a@2x.jpg)

'개발 관련 학습정리 > AVR(atmega128) Register 분석' 카테고리의 다른 글

| [Atmega128] 9. I2C 통신 (Inter-Integrated Circuit) (2) | 2019.08.05 |

|---|---|

| [Atmega128] 8. UASRT 통신 (Universal Synchronus Receiver Transmit) (5) | 2019.08.05 |

| [Atmega128] 6. 아날로그 변환기 ADC (Analog to Digital Converter) (0) | 2019.08.05 |

| [Atmega128] 5. 아날로그 비교기 (Analog Comparator) (0) | 2019.08.03 |

| [Atmega128] 4. 타이머 인터럽트 (clk/Timer mode/OC 단자 출력) (0) | 2019.08.03 |